| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | Quiz | Index |

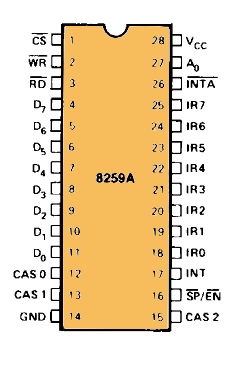

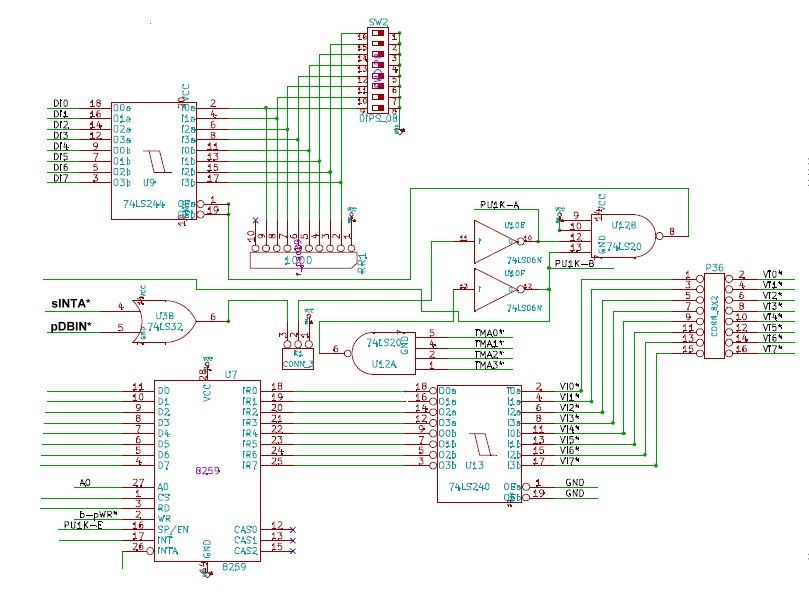

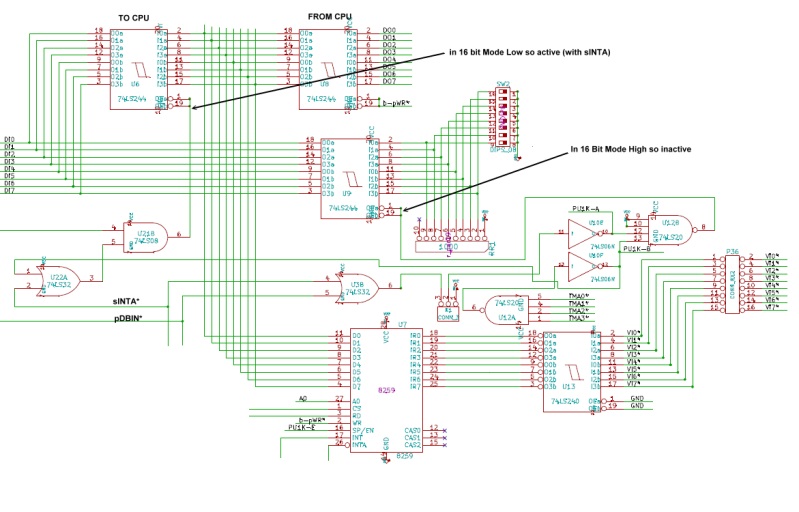

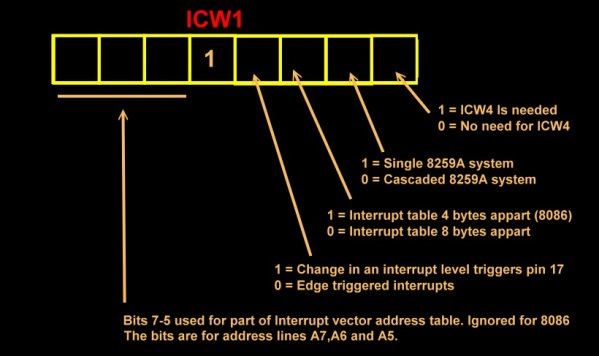

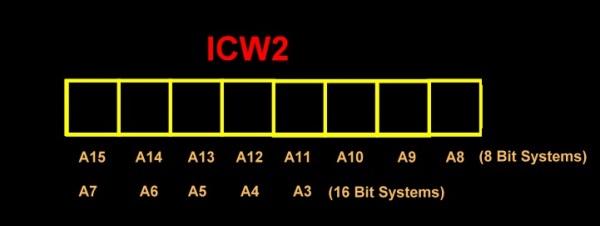

Lets first see how the 8259A works with an 8080 CPU. Please see the attached 8259A data sheet. The chip has 8 interrupt input pins. When any one of these is triggered it MAY (depending on how the chip is programmed), pull the 8080 interrupt line low. When this happens the 8080 will finish its current instruction and if interrupts are enabled in software acknowledge to the 8259 it got the interrupt request by sending a signal from its INTA pin which goes directly to the 8259. Immediately after receiving this INTA signal the 8259 will put on the 8080 data bus a JUMP instruction (C3H). The 8080 will then send two more INTA signals whereupon the 8259 will place low byte and high byte of data (programmed into the 8259) on to the data bus so that the 8080 sees these bytes as a JMP to a location XXXXH. As far as the 8080 is concerned, the data bus appears to it as if it read memory asking for a JMP to a new location. At that location is software to handle the interrupt request. A return at the end of this software returns the CPU to where it was before the interrupt. The 8259 meanwhile is busy looking/processing any more interrupts.

Lets first see how the 8259A works with an 8080 CPU. Please see the attached 8259A data sheet. The chip has 8 interrupt input pins. When any one of these is triggered it MAY (depending on how the chip is programmed), pull the 8080 interrupt line low. When this happens the 8080 will finish its current instruction and if interrupts are enabled in software acknowledge to the 8259 it got the interrupt request by sending a signal from its INTA pin which goes directly to the 8259. Immediately after receiving this INTA signal the 8259 will put on the 8080 data bus a JUMP instruction (C3H). The 8080 will then send two more INTA signals whereupon the 8259 will place low byte and high byte of data (programmed into the 8259) on to the data bus so that the 8080 sees these bytes as a JMP to a location XXXXH. As far as the 8080 is concerned, the data bus appears to it as if it read memory asking for a JMP to a new location. At that location is software to handle the interrupt request. A return at the end of this software returns the CPU to where it was before the interrupt. The 8259 meanwhile is busy looking/processing any more interrupts.| RST# | OP Code | Bit Pattern | RAM Location | |

| RTS 0 | C7 | 11000111 | 0000H | |

| RST 1 | CF | 11001111 | 0008H | |

| RST 2 | D7 | 11010111 | 0010H | |

| RST 3 | DF | 11011111 | 0018H | |

| RST 4 | E7 | 11100111 | 0020H | |

| RST 5 | EF | 11101111 | 0028H | |

| RST 6 | F7 | 11110111 | 0030H | |

| RST 7 | FF | 11111111 | 0038H |

This page was last modified on 06/03/2011